CPU의 수행하는 세부적 동작들

- 명령어 인출(IF) : 기억장치로부터 명령어를 읽음

- 명령어 해독(ID) : 수행해야 할 동작을 결정하기 위해 명령어를 해독

- → 명령어 인출과 해독은 모든 명령어들에 대해 공통적으로 수행

- 데이터 인출(DF) : 명령어 실행을 위해 데이터가 필요한 경우, 기억장치 || I/O장치(키보드)로부터 그 데이터를 읽음

- 데이터 처리(DP) : 데이터에 대한 산술적 혹은 논리적 연산을 수행

- 데이터 저장(DS) : 수행한 결과를 저장

- → 데이터 인출, 처리, 저장은 필요한 경우에만 수행

명령어를 인출 했는데, 오퍼랜드가 데이터 주소가 아닌 데이터라면 데이터 인출 과정 필요 X

++ 순서 변경할 때도 데이터 인출 필요 X

CPU 기본 구조

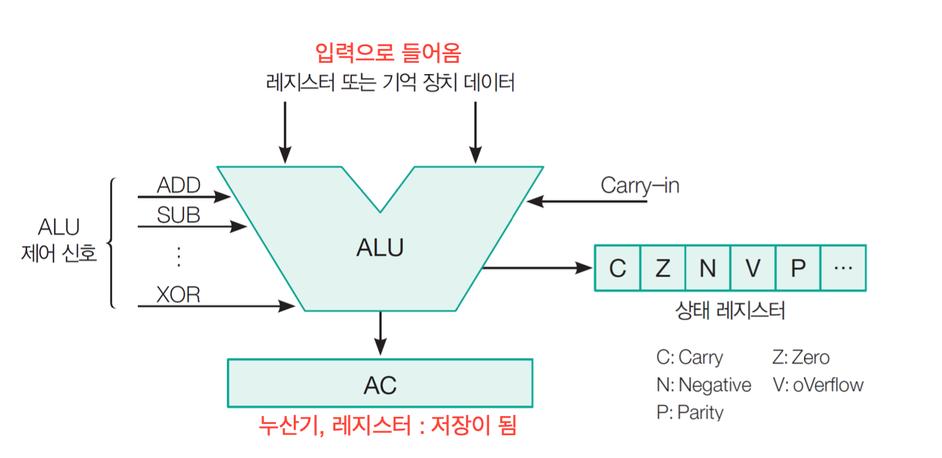

- 산술논리연산장치 (ALU)산술 연산 : 사칙연산 등

논리연산 : AND OR NOT XOR..

: 각종 산술 연산들과 논리 연산들을 수행하는 회로들로 이루어진 하드웨어 모듈 - 레지스터 세트

- CPU 내부에 위치한 기억장치로, 액세스 속도가 가장 빠른 기억장치

- CPU가 사용하는 데이터와 명령어를 신속하게 읽기, 저장, 전송에 사용

- CPU 내부에 포함할 수 있는 레지스터들의 수가 제한됨

- 특수 목적용 레지스터와 적은 수의 일반 목적용(데이터, 범용) 레지스터

- 누산기 (AC) : 중간 값 기억

- 프로그램 카운터 (PC) : MM의 다음 주소 기억

- 명령어 레지스터 (IR) : MBR로부터 명령어 기억

- 메모리 버퍼 레지스터 (MBR) : CPU와 MM 사이의 버퍼

- 메모리 주소 레지스터 (MAR) : CPU와 MM 사이의 주소 버퍼

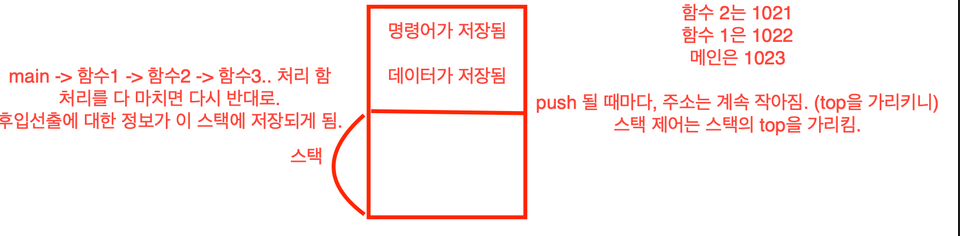

- 스택 포인터 (SP) : 인터럽트로부터 PC 정보 보관

- 인덱스 레지스터 (IX) : ?

- 제어 유니트

: 명령어를 해석하고, 그것을 실행하기 위한 제어 신호들을 순차적으로 발생하는 하드웨어 모듈 - CPU 내부 버스

- ALU와 레지스터 간의 데이터를 전달하는 데이터 선들과 제어 유니트에서 발생되는 제어 신호를 전달하는 선들로 구성

- 외부의 시스템 버스들과는 직접 연결 X, 반드시 버퍼 레지스터(MBR, MAR)들 혹은 시스템 버스 인터페이스 회로를 통해 시스템 버스와 접속

명령어 싸이클

: CPU가 한 개의 명령어를 실행하는데 필요한 전체 처리 과정

CPU가 프로그램 실행을 시작한 순간부터 전원을 끄거나 회복 불가 오류로 중단될 때까지 반복

두 개의 부사이클들로 분리

- 인출 사이클(Fetch) : CPU가 기억장치로부터 명령어를 읽어오는 단계

- 실행 사이클 (Execution) : 명령어를 실행하는 단계

명령어 실행에 필요한 CPU 내부 레지스터들

프로그램 카운터(PC)

- 다음에 인출할 명령어의 주소를 가지고 있는 레지스터

- 각 명령어가 인출된 후, 자동으로 일정 크기(한 명령어 길이, 단어 / 주소지정단위)만큼 증가

- 분기(Branch) 명령어가 실행되는 경우 목적지 주소로 갱신 (인터럽트..)

누산기(AC)

- 데이터를 일시적으로 저장하는 레지스터

- ALU의 산술 연산과 논리 연산과정에 사용됨

- 누산기 레지스터의 길이는 CPU가 한 번에 처리할 수 있는 데이트 비트 수(단어길이)와 동일

- 단어 : 64bit, 주소지정단위 : 16bit ⇒ PC ← PC + 4

명령어 레지스터(IR)

- 가장 최근에 인출된 명령어 코드가 저장되어 있는 레지스터

- ‘제어 장치’는 IR에서 명령어를 읽어와 해독하고 명령을 수행하기 위해 컴퓨터 각 장치에 제어신호 전송

기억장치 주소 레지스터(MAR)

: PC에 저장된 명령어 주소가 시스템 주소 버스로 출력되기 전, 일시적으로 저장되는 주소 레지스터

기억장치 버퍼 레지스터(MBR || MDR)

: 기억장치에 쓰여질 데이터 혹은 기억장치로부터 읽혀진 데이터를 일시적으로 저장하는 버퍼 레지스터

데이터 버스는 양방향인데, 모두 MBR을 거침

기타 CPU 내부 레지스터

- 데이터 레지스터(범용 레지스터) : CPU 내 데이터를 일시적으로 저장하기 위한 레지스터

- 입출력 주소 레지스터(I/O AR) : 특정 I/O 장치의 주소를 지정하는데 사용

- 입출력 버퍼 레지스터(I/O BR) : I/O모듈과 CPU 간에 데이터를 교환하는데 사용

- 스택 제어 레지스터(SP) : 메모리 한 블록이며, 데이터는 후입 선출(LIFO), 복귀할 주소 정보를 저장

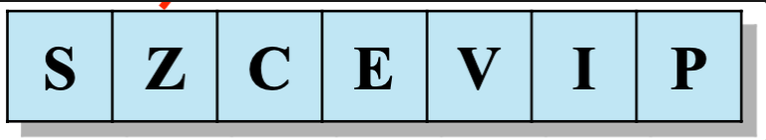

5. 상태 레지스터(SR, ALU 안에 있음)

- CPU가 작동하는 동안 특정 조건의 발생을 표시하는데 사용됨

- 1Byte || 2Byte인 특수 목적용 레지스터

- 명령어 실행 결과에 따른 조건 플래그들 저장

- 플래그 레지스터 || 프로그램 사애 워드라고도 함

조건 플래그 종류

- 부호(S) 플래그 : 직전에 수행된 산술연산 결과값의 부호 비트를 저장(양수 0, 음수 1)

- 제로(Z) 플래그 : 연산 결과값이 0이면, 1로 지정

- 올림수(C) 플래그 : 덧셈 || 뺄셈에서 올림수나 빌림수가 발생한 경우 1로 지정

- 동등(E) 플래그 : 두 수를 비교한 결과가 같게 나왔을 경우에 1로 지정

- 오버플로우(V) 플래그 : 산술연산 과정에서 오버플로우가 발생한 경우 1로 지정

- 인터럽트(I) 플래그 : 인터럽트 가능 상태이면 0으로, 불가능이면 1로 지정

- 슈퍼바이저(P) 플래그 : CPU의 실행 모드가 슈퍼바이저모드이면 1로, 사용자 모드면 0으로

'🖥️ Computer Science > Computer Architecture' 카테고리의 다른 글

| [컴퓨터 구조] CPU의 구조와 기능 2 (1) | 2023.11.12 |

|---|---|

| [컴퓨터 구조] 컴퓨터 시스템 개요 2 (1) | 2023.11.12 |

| [컴퓨터 구조] 컴퓨터 시스템 개요 1 (1) | 2023.09.21 |